#### DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING EE6602- EMBEDDED SYSTEMS QUESTION BANK UNIT I - INTRODUCTION TO EMBEDDED SYSTEMS PART A

## 1. Define system.

A system is a way of working, organizing or doing one or series of tasks by following a fixed plan, program and set of rules.

2. What are the typical characteristics of an embedded system? )(apr/may2017)

T ypical characteristics:perform a single or tightly knit set of functions; increasingly highperformance & real-time constrained; power, cost and reliability are often important attributes that influence design;Application specific processor design can be a significant component of some embedded systems.

# 3. What is the need of watchdog timer?(may/june 2016)

Watchdog timer is a timer that resets the processor in case the program gets stuck for an unexpected length of time.

4.What are the challenges faced in designing an embedded system? (nov/dec 2016) (may/june 2016)

- <sup>□</sup> Amount and type of hardware needed.

- <sup>□</sup> Clock rate reduction

- □ Voltage reduction

- Process deadlines'

- □ Flexibility and upgrade ability

- <sup>□</sup> Wait, stop and cache disable instructions.

## 5. When do we need an RTOS?

RTOS has a basic function of the OS plus functions for real time task scheduling and interrupt latency control. It uses the timers and system clocks, time allocation and de-allocation to attain best utilization of the CPU time under the given timing constraint for the task. 6.Name some processor in complex embedded system?

General purpose microprocessor Microcontroller Single purpose Dual core processor 7. What are the abstractions steps in design process? (nov/dec 2016)(apr/may2017)

- <sup>D</sup> Requirements

- Specifications

- Architecture

- <sup>D</sup> Components

- □ System integration

- 8. What are the classification of ES?

- □ Small scale embedded system

- <sup>□</sup> Medium scale embedded system

- <sup>□</sup> Sophisticated embedded system

- 9. What are the tools used for programming tools are used in a complex software design?

- □ RTOS

- <sup>□</sup> Source code engineering tool

- □ Simulator

- Debugger

- □ Assembler

- <sup>□</sup> Integrated development environment

- 10.Name some hardware components used in embedded system.

- Power source

- <sup>□</sup> Clock oscillator circuit

- <sup>□</sup> Crystal resonator

- □ External oscillator IC

- □ Real time clock

- Memories

#### UNIT II - EMBEDDED NETWORKING PART A

#### 1. What is CAN bus?(apr/may2017)

It is a standard bus used at the control area network generally in automotive and industrial electronics.

#### 2. What is COM port?

It is a port at the computer where a mouse, modem, serial printer or mobile serial printer connects for serial I/O in UART mode and there are handshaking signals for exchange of signals before UART mode communications.

#### 3.Define device driver. (nov/dec 2016)(apr/may2017)

A device driver is a software for controlling receiving and sending byte or stream of bytes from or to a device.Device is a unit that has a processing element and that connects to the processor of embedded system internally or through the port or bus. It has fixed pre assigned port addresses according to its interfacing or bus controller circuit.

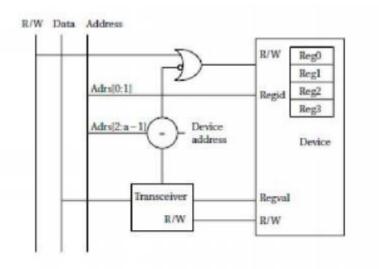

4. what is device decoder?

It is a circuit to take the system address bus signal as the input and generate a device select signals CS, for the port address selection during the device read or write instruction of the system processor.

#### 5. What is an I/O port?

It is port for input or output operations at an instance. Handshake input and handshake output also known as I/O ports. For examples, a keypad is said to connect to an I/O port. 6. Define protocol.

Protocol is a way of transmitting messages on a network by using software for adding the additional bit such as starting bits, header, addresses of source and destination, error control bit and ending bits.

#### 7. Define bus.

Bus is a set of parallel lines which carry signals from one to another unit. Bus enables interconnecting among many units in a simple way. The signal specific sequences according to a method or protocol.

#### 8. What is the need of timing diagram?

Timing diagram reflects the relative time intervals of the signals on the external buses with respect to the processor clock pulses.

9. What are the types of architecture model?

- <sup>□</sup> Single level architecture

- <sup>□</sup> Two-level architecture

- <sup>D</sup> Multi-level architecture

10.Mention some metrics of a bus.

- Simplifies number of interconnections compared to direct connections between one another.

- <sup>□</sup> Provides a common way of interconnecting different or same type of I/O devices.

- <sup>□</sup> Can add a new device or system interface that is compatible with a system I/O bus.

# UNIT III - EMBEDDED FIRMWARE DEVELOPMENT ENVIRONMENT PART A

1. What is EDLC?

Embedded produce development life cycle is an analysis design implementation based standard problem solving approach for embedded product development.

- 2. What are the objective of EDLC?

- <sup>°</sup> Ensure that high quality products are delivered to end user.

- ° Risk minimization

- ° Maximize the productivity

## 3. What are the different phases of EDLC? Apr/may2017

- <sup>1.</sup> Need

- <sup>2.</sup> Conceptualization

- <sup>3.</sup> Analysis

- <sup>4</sup>. Design

- <sup>5.</sup> Development and testing

- <sup>6.</sup> Deployment

- <sup>7.</sup> Support

- <sup>8.</sup> Upgrades

- <sup>9.</sup> Retirement

4. What is meant by conceptualization?

It is the product concept development phase and it defines the scope of the concept, performs cost benefits analysis and feasibility study and prepare project management and risk management.

5. What is upgrade phase?

The upgrade phase of product development deals with the development of upgrades for the product which is already present in the market.

6. What is prototyping model?

Prototyping model is a EDLC model which is the variation of the iterative model in which a more refined prototype is produced at the end of each iteration.

7. What is DFG model?

The data flow graph model translates the data processing requirements into a flow graph. It is data driven model in which the program execution is determined by data.

8. What is sequential program model?

In sequential programming model, the functions or processing requirements are executed in sequence. It is same as the conventional procedural programming.

9. What is object oriented model?

It is an object based model for modeling system requirements. It divides complex software requirements into simple well defined pieces called objects.

10. What is state machine model?nov/dec2016

The state machine model contain a number of states are finite. In other words the system is described using a finite number of possible states.

#### <u>UNIT IV - RTOS BASED EMBEDDED SYSTEM DESIGN</u> <u>PART A</u>

1. What is an operating system?

The operating system acts as a bridge between the user applications and the underlying system resources through a set of system functionalities and services.

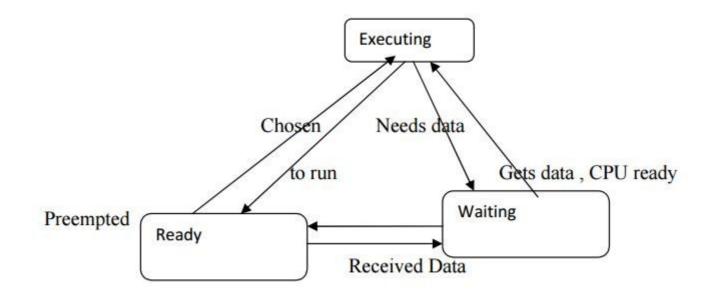

2.What is preemptive and nonpreemptive scheduling?nov/dec2016

Under nonpreemptive scheduling once the CPU has been allocated to a process, the process keeps the CPU until it releases the CPU either by terminating or switching to the waiting state. Preemptive scheduling can preempt a process which is utilizing the CPU in between its execution and give the CPU to another process.

3. What is thread in the operating system context?may/june2016

A thread is the primitive that can execute code. A thread is a single sequential flow of control within a process. Thread is also known as light weight process.

4. What are the various multi tasking models? May/june2016

- <sup>□</sup> Co-operative multitasking

- Preemptive multitasking

- Non-preemptive multitasking

- 5. What is co-operative multitasking?

It is a multitasking model in which a task/process gets a chance when the currently executing task relinquishes the CPU voluntarily.

6. What are the different queues associated with process scheduling?

- □ Job queues

- Ready queues

- Device queues

7. What are the types of non-preemptive scheduling?

- 1. First come first served

- 2. Last come last served

- 3. Shortest job first

- 4. Priority based

#### 8. What is pipe?

Pipe is a selection of the shared memory used by processes for communicating. Pipes follow the client server architecture.

#### 9. What is IPC?

The mechanism through which processes/task communicate each other is known as inter process communications.

It is essential for process co-ordination.

10. What is deadlock?

Deadlock is a situation where non of the processes are able to make any progress in their execution. It is the condition in which a process is waiting for a resources held by another process which is waiting for a resource held by the first process. Livelock is a condition where a process always does something but is unable tp make any progress in the execution completion

## **UNIT V - EMBEDDED SYSTEM APPLICATION DEVELOPMENT**

# PART A

## 1. Define MUCOS.

MUCOS is a portable, ROMable, Scalable, real time and multitasking kernel. It is used over thousands of applications including automotive, avionics, consumer electronics, medical devices, military aerospace networking.

- Cameras

- Automotive

- Medical devices

- Aerospace

## 2.What is AVCM?

Automatic chocolate vending machine is a machine using which the children can automatically purchase the chocolates. The payment is made by inserting the coins of appropriate amount into a win slot.

- 3.What are the three phases of washing machine? Wash phase

- Spin phase

- Rinse phase

Automotive embedded system are normally built around microcontroller or DSP or a hybrid of the two and are generally known as electronic control units.

- 5. What are the classifications of ESU?

- High speed electronic control unit

- Low speed electronic control unit

- 6.What is the use of HECU?

High speed electronic control unit are deployed in critical control units requiring fast response like fuel injection system, antilock brake system.

7. What is the use of LEC?

Low speed electronic control unit are deployed in applications where response time is not so critical. They are generally built around low cost microprocessor and DSP. Audio controller, passenger and driver door lock are the examples of LEC.

- 8.Name some serial buses used in automotive communication.apr/may2017

- Controller area network

- <sup>□</sup> Local interconnect network

- Media oriented system transport bus

- 9. What are the key players of the automotive embedded marker?

- Silicon providers

- <sup>□</sup> Tools and platform providers

- <sup>D</sup> Solution providers

10.What are the applications of an embedded system?nov/dec2016, apr/may2017

- 1. Consumer electronics, e.g., cameras, camcorders,

- 2. Consumer products, e.g., washers, microwave ovens,

- 3. Automobiles (anti-lock braking, engine control,

- 4. Industrial process controllers & avionics/defense

#### UNIT-1

# **1.** Discuss about the structural units in embedded processor and how a processor is selected for an embedded application?

# **EMBEDDED SYSTEM CONSTRAINTS:**

#### Processor

Processor is the heart of the embedded system. It consists of two units:

**Two Essential Units: Operations**

Control Unit (CU), Fetch

**Execution Unit (EU) Execute-** It includes ALU and executes the program task, say, halt, interrupt

and jump or another set of instructions

Processor runs the cycle of fetch and execute. Processor mostly in the form of IC or in the form of Core ASIP [Application Specific Instruction Processor] or Soc [System on Chip], core means a part of functional circuit on VLSI chip.

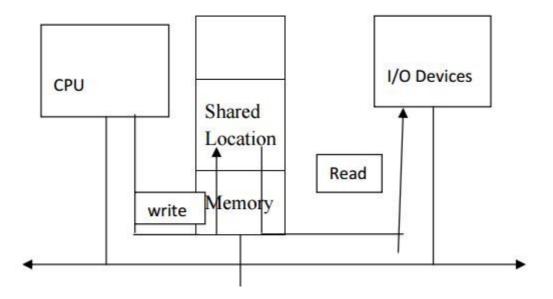

# 2. With a neat diagram, explain the working of Direct Memory Access (DMA)?

## **Embedded hardware components**

- Microcontroller or ASIP (Application Specific Instruction Set Processor)

- RAM for temporary variables and stack

- ROM for application codes and RTOS codes for scheduling the tasks

- EEPROM for storing user data, user address, user identification codes, card number and expiry date

- Timer and Interrupt controller

- A carrier frequency ~16 MHz generating circuit and Amplitude Shifted Key (ASK)

- Interfacing circuit for the I/Os

- Charge

# Embedded Software

- Boot-up, Initialisation and OS programs

- Smart card secure file system

- Connection establishment and termination

- Communication with host

- Cryptography

- Host authentication

- Card authentication

- Addition parameters or recent new data sent by the host (for example, present balance left)

# **Smart Card OS Special features**

- Protected environment.

- Every method, class and run time library should be scalable.

- Code-size generated be optimum.

- Memory should not exceed 64 kB memory.

- Limiting uses of specific data types; multidimensional arrays, long 64-bit integer and floating

pointsSmart Card OS Limiting features \_ Limiting uses of the error handlers, exceptions, signals,

serialization, debugging and profiling. [Serialization means process of converting an object is converted

into a data stream for transferring it to network or from one process to another. At receiver end there is

de-serialization.]

## Smart Card OS File System and Classes

Three-layered

# **ROM image, Programming Languages and Program models ROM Image**

• Final stage software also called ROM image

\* (Just as an image is a unique sequence and arrangement of pixels, embedded software is also a unique

placement and arrangement at each ROM address of bytes for instructions and data. ) System

# ROM memory embedding the software, RTOS, data, and vector addresses Final machine software

Bytes at each address defined for creating the ROM image.

By changing this image, the same hardware platform work differently and can be used for entirely

# 3.Explain the memory management method in detailed manner?

# a. Functions Assigned to the ROM or EPROM or Flash

- 1. Storing 'Application' program from where the processor fetches the instruction codes

- 2. Storing codes for system booting, initializing, Initial input data and Strings.

- 3. Storing Codes for RTOS.

- 4. Storing Pointers (addresses) of various service routines.

# b. Functions Assigned to the Internal, External and Buffer RAM

- 1. Storing the variables during program run,

- 2. Storing the stacks,

- 3. Storing input or output buffers for example, for speech or image .

# c. Functions Assigned to the EEPROM or Flash

Storing non-volatile results of processing

## d. Functions Assigned to the Caches

1. Storing copies of the instructions, data and branch-transfer instructions in advance from external memories and

2. Storing temporarily the results in write back caches during fast processing

## (v) Interrupts Handler

Interrupt Handling element for the external port interrupts, IO interrupts, timer and RTC interrupts, software interrupts and Exceptions

# (vi) Linking Embedded System Hardware

• Linking and interfacing circuit for the Buses by using the appropriate multiplexers, and decoders,

demultiplexers Interface the various system units

# **<u>4. Explain the I/O Communication ports in detailed manner?</u>**

**a.** Communication Driver(s) Network Ethernet or serial driver to communicate with host embedded system Expansion

□ Facility Serial Bus(es):

For example, UART (512 kbaud/s), 1-wire CAN (33 kbps),

Industrial I2C (100kbps), SM I2C Bus (100 kbps), SPI (100 kbps), Fault tolerant CAN (110 kbps),

Serial Port (230 kbps), MicroWire (300 kbps). SCSI parallel (40 Mbps), Fast SCSI (8M to 80 Mbps), Ultra SCSI-3 (8M to 160 Mbps), FireWire/IEEE 1394 (400 Mbps, 72 meter), High Speed USB 2.0 (480 Mbps, 25 meter) Parallel Bus(es): PCI, PCI-X

- b. Media IO Control Element

- c. Keypad or Keyboard IO Interface

- d. LCD Display System Interface

- e. ADC Single or Multi channel

- f. DAC

- g. GPIB Interface Element

- h. Pulse Dialing Element

- i. Modem and j. Bluetooth, 802.11, IrDA.

# 5.Explain the Basic Circuit Elements at the Embedded control System?

## (i) Power Source

1. System own supply with separate supply rails for IOs, clock, basic processor and memory and

analog units, or

2. Supply from a system to which the embedded system interfaces, for example in a network card,

## OR

Charge pump concept used in a system of little power needs, for examples, in the mouse or contactless

#### smart card

## **Power Dissipation Management**

- 1. Clever real-time programming by Wait and Stop instructions

- 2. Clever reduction of the clock rate during specific set of instructions

- 3. Optimizing the codes and

- 4. Clever enabling and disabling of use of caches or cache blocks

## (ii) Clock Oscillator Circuit and Clocking Units

- 1. Appropriate clock oscillator circuit

- 2. Real Time Clock\*( System Clock) and Timers driving hardware and software

## (iii) Reset Circuit

- 1. Reset on Power-up

- 2. External and Internal Reset circuit

- 3. Reset on Timeout of Watchdog timer

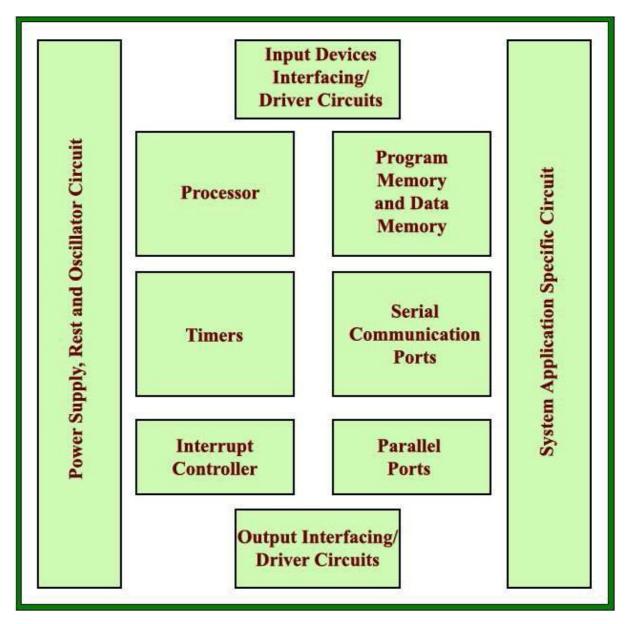

# components of embedded system

## • It has Hardware

Processor, Timers, Interrupt controller, I/O Devices, Memories, Ports, etc.

## • It has main Application Software

Which may perform concurrently the series of tasks or multiple tasks.

#### • It has Real Time Operating System (RTOS)

RTOS defines the way the system work. Which supervise the application software. It sets the rules during the

execution of the application program. A small scale embedded system may not need an RTOS.

## **6.Discuss about the memory devices in clear manner?**

Memory is an essential part of all microprocessor based systems. Different memory types are available to suit

different tasks. Some of these memory types will be discussed here.

# random access memory (ram)

This is memory that can be written to and read from as often as we wish. The 'Random Access' refers

to the fact that we can access any position in the memory equally fast. RAM is used for short term storage, such

as for storing variables that are used by a program. RAM is volatile memory. It will only store contents (at best)

for as long as the power is applied.

# ram signals

A typical RAM device will have (at least) the following set of signals:

**Data Bus:** This is a set of lines which carry the data into the memory or out of it. We refer to the width of the memory by how many bits can be written or read simultaneously.

Address Bus: This is a set of lines which is used to specify the location of the data to be read/written.

WR line: This line tells the RAM it is going to be written to or read from.

**OE line:** This line enables the data bus as output for when we read data from the device.

**CS line:** This line is used to select the device. This line enables or disables the entire chip.

Typical timing diagrams may be found in the lab sheet.

# **Basic RAM Types**

i. dram

Dynamic RAM uses tiny capacitors to store each bit of information. This is a cheap, high density

technology. The capacitors need to be recharged periodically and so DRAM needs to be refreshed frequently.

DRAM forms the basis for most computer memory. Usually DRAM is used together with a DRAM controller

which handles the refresh cycles.

# ii. sram

Static RAM uses a flip flop to store each bit in the memory. Because the data is stored in a proper flip

flop there is no need to refresh SRAM. SRAM is more expensive and lower density than DRAM.

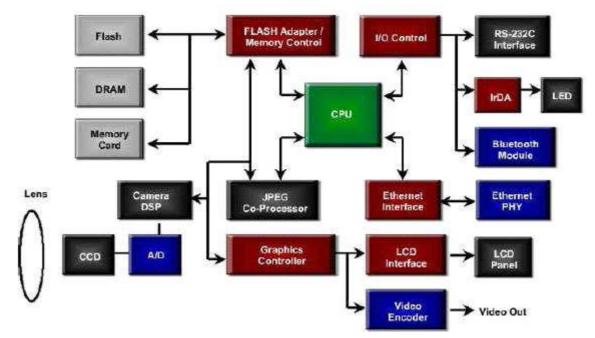

# 7. Explain any one of the processor in detailed manner (ASSP)?

• ASSP is dedicated to specific tasks and provides a faster solution.

• An ASSP is used as an additional processing unit for running the application in place of using embedded

software.

# Examples: IIM7100, W3100A

Typically a set top box processor or mpeg video-processor or network application processor or

mobile application processor

# Single purpose processor or Application Specific Instruction processor

- Floating point Coprocessor

- CCD Pixel coprocessor and image codec in digital camera

- Graphic processor

- Speech processor

- Adaptive filtering processor Encryption engine

- Decryption engine

- Communication protocol stack processor

- Java accelerator

# **Use of Accelerator Cores:**

# Examples

Java Accelerator *Nazonin Communications* Java codes run 15 to 60 Times fast, Video Accelerator for fast Video Processing

# Multi core processors or multiprocessor system using GPPs

## Examples

- Multiprocessor system for Real time performance in a video-conference system,

- Embedded firewall cum router,

- High-end cell phone.etc.

# MOORE'S LAW

- Moore's law describes a long-term trend in the history of computing hardware.

- Since the invention of the integrated circuit in 1958, the number of transistors that can be placed

inexpensively on an integrated circuit has increased exponentially, doubling approximately every two

years.

• The trend was first observed by Intel co-founder Gordon E. Moore in 1965.

• Almost every measure of the capabilities of digital electronic devices is linked to Moore's law: processing

speed, memory capacity, etc.

# **8.BASIC COMPONENTS OF EMBEDDED SYSTEMS**

## **Design Issues**

- Cost

- I/O capability

- Size

- Power consumption

- On-Chip memory

- Performance

- Software

- Instruction set

- Development tools

- Testability and reliability

- Analog components

- Sensors, controllers,

- Digital components

- Processor, coprocessors

- Memories

- Controllers, busses

- ASIC: Application-Specific Integrated Circuit, a chip designed

- for a particular application

- Converters A/D, D/A, ...

- Software

Application programs

Exception handlers

# **Design Metrics**

- Unit cost the \$ cost for each unit excluding development cost

- NRE cost: \$ cost for design and development

- Size: The physical space reqd. determined by bytes of sw, number of gates and transistors in hw

- Performance: execution time or throughput of the system

- Power: lifetime of battery, cooling provisions

- Flexibility: ability to change functionality without heavy NRE cost

## **Application Specific Characteristics**

- Application is known before the system is designed

- System is however made programmable for

- Feature upgrades

- Product differentiation

- Often application development occurs in parallel to system development

- Hw-Sw partitioning should be as delayed as possible

- For upgrades design reuse is an important criterion

## 9.Detailed about the Programmable Logic Technologies?

Programmable logic is used to build up complex circuits without the need to connect up many gates.

They consist of chips which contain many logic gates. The way in which these gates are connected is

determined by the way in which the device is configured (programmed).

Programmable logic is commonly used because it is more compact and generally can run faster than a

circuit made out of discrete gates. Programmable logic offers design security.

There has been remarkable progress in the development of programmable logic devices over the last

few years. Because of the vast changes that the industry has seen there are very few standards in terms of signals and compatibility between devices.

#### PAL (Programmable Array Logic) and PLA (Programmable Array Logic)

These were the earliest form of programmable logic. They had a simple grid type structure which was

programmed by blowing fuses. They were only programmable once. The programming was done in a simple

language, typically PALASM, ABEL or CUPL.

## GAL (Generic Array Logic)

Slightly more complex and flexible structure than PAL. Reprogrammable! They typically had a

JTAG (Joint Test and Access Group) interface for programming. This is an industry standard (IEEE1149.1)

four wire interface that has become one of the dominant programming and debugging interfaces for

programmable logic, microcontrollers and larger processors.

**PEEL (programmable electrically erasable logic)**

Very similar to GALs, but made of CMOS rather than bipolar technology.

## **CPLD (Complex Programmable Logic Device)**

These devices are typically made up of many small PAL's connected together with a programmable

interconnection system. They are much more flexible than any of the previous programmable logic families.

# **FPGA (Field Programmable Gate Array)**

These are the high end of the market. They consist of lots of programmable logic blocks. These blocks

are each quite complex, typically consisting of PAL type logic as well as devices such as configurable flip flops.

They are available in sizes up to several million gates.

They often have peripherals such as phase locked loop clock multipliers, memory blocks and communication (LVDS) systems.

There are many FPGA's which are big enough to hold entire microprocessors. These are becomingmore popular. They are called "soft cores".

## **10.Detailed about the Watchdog timer in clear manner?**

A timing device such that it is set for a preset time interval and an event must occur during that interval else the device will generate the timeout signal on failure to get that event in the watched time interval. On that event, the watchdog timer is disabled to disable generation of timeout or reset Timeout may result in processor start a service routine or start from beginning

# Watchdog timer application

• An application in mobile phone is that display is off in case no GUI interaction takes place within a watched time interval.

• The interval is usually set at 15 s, 20 s, 25 s, 30 s in mobile phone.

• This saves power. An application in temperature controller is that if controller takes no action to switch off the current within preset watched time interval, the current is switched off and warning signal is raised as indication of controller failure. Failure to switch off current may burst a boiler in which water is heated.

## Provisioning of watchdog timer

A software task can also be programmed as a watchdog timer Microcontroller may also provide for a watchdog timer.

68HC11 microcontroller watchdog timer 68HC11 microcontroller watchdog timer There are two registers, CONFIG (system configuration control register) and COPRST (computer operating properly and processor reset on failure).

They are for programming the interrupts of the watchdog timer.CONFIG has a bit, NOCOP. It configures when processor writes the configuration word at the address 0x003F. NOCOP is the 2nd bit of CONFIG If NOCOP is reset to 0 the COP facility is enabled. [COP means computer (68HC11 watchdog timer operating properly]. COP facility provides for keeping a watch on the user program execution timeWatchdog timer overflows (time outs) Watchdog timer overflows (time outs) 68HC11 program counter is reset according to the 16 bits (lower and higher bytes) preloaded at the addresses 0xFFFA and 0xFFFB, respectively.

If these 16 bits are the same as the bits in 0xFFFE and 0xFFFF, then the microcontroller executes instructions as when it resets on power up or else executes the routine at the 16-bit address fetched from 0xFFFE and 0xFFFF on failure within the watched time interval. A watchdog timer number of applications • It is timing device such that it is set

for a preset time interval and an event must occur during that interval and program instuction must disable the watchdog timer else the device will generate on the timeout signal an interrupt for the failure to get that event in the watched time interval.

#### <u>UNIT II</u>

#### **<u>1.Write short notes about the I2C in detailed manner?</u>**

The Bus has two lines that carry its signals— one line is for the clock and one is for bi-directional data. There is a standard protocol for the I 2C bus.

Device Addresses and Master in the I Device Addresses and Master in the I2C bus Each device has a 7-bit address using which the data transfers take place. Master can address 127 other slaves at an instance. Master has at a processing element functioning as bus controller or a microcontroller with I 2C (Inter Integrated Circuit) bus interface circuit.

Slaves and Masters in the I Slaves and Masters in the I2C bus Each slave can also optionally has I 2C (Inter Integrated Circuit) bus controller and processing element. **Number of masters can be connected on the bus**.

However, at an instance, master is one, which initiates a data transfer on SDA (serial data) line and which transmits the SCL (serial clock) pulses. From master, a data frame has fields beginning from start bit

#### Synchronous Serial Bus Fields and its length

First field of 1 bit- Start bit similar to one in an UART

Second field of 7 bits — address field. It defines the slave address, which is being sent the data frame (of many bytes) by the master

Third field of 1 control bit— defines whether a read or write cycle is in progress Fourth field of 1 control bit— defines whether is the present data is an acknowledgment (from slave)

Fifth field of 8 bits - I 2C device data byte

Sixth field of 1-bit— bit NACK (negative acknowledgement) from the receiver. If active then acknowledgment after a transfer is not needed from the slave, else acknowledgement is expected from the slave

Seventh field of 1 bit – stop bit like in an UART.

#### **Disadvantage of I 2C bus**

• Time taken by algorithm in the hardware that analyzes the bits through I 2C in case the slave hardware does not provide for the hardware that supports it.

- Certain ICs support the protocol and certain do not.

- Open collector drivers at the master need a pull-up resistance of 2.2 K on each line.

# 2.Write short notes about the RS232C in detailed manner?

# **RS - 232C**

The TTL logic signals are not what is transmitted between equipment such as modems

computers and terminals. One standard that describes the signals for communicating is the

RS-232C standard.

This standard causes as much trouble as any standard you can name because it deals with two types of equipment, data communications equipment (DCE) and data terminal equipment (DTE).

• Typically, a modem is DCE and a terminal or computer is DTE.

• The problem is that the cable to connect DCE to DTE is different from the cable to connect DTE to DTE.

• Also, nonstandard use of the control signals is a problem.

• Murphy's law says that if you need to connect to a serial port, you always have the wrong cable.

• RS-232C specifies 25 signal pins with a – male DTE connector and – a female DCE connector.

• Most of these signals are not used in most applications so a 9 pin subset is used. – Actually in some cases, only three wires are used.

• The mark and space signals are inverted by the standard to the following levels: A logic high or mark is between -3 V and -15 V under load A logic low or space is between +3 V and +15 V under load.

• Typically, +12 and -12 volts are used.

• The voltage swing is > the TTL 5 volts for noise immunity.

RS-232C interface TTL levels RS-232C levels MC1489A line receiver MC1488 line driver Signal Conversion to and from TTL and RS-232C levels.

# Signal meanings - RS232

Transmit data group – TD – transmit data – data from DTE to DCE – RTS – ready to send – DTE asserts before sending data and waits for CTS before sending – CTS – clear to send – DCE sends in response to RTS

• Receive data group – TD – transmit data – data from DCE to DTE – DSR – data set ready – DCE asserts before sending data and waits for DTR before sending – DTR – data terminal ready– DTE sends in response to DSR – CD – carrier detect – modem is receiving a carrier from a modem at other end

• SG - signal ground - common return for all lines

• Note: Not all manufacturers use the control lines

Connecting DTE to DCE equipment uses a straight through cable with wires connected to the proper pins. A DTE to DTE connection requires a null modem cable. Baud: bits per second Baud Application 110 ASR-33 Teletype 300 Early acoustic modems 1200 Direct-coupled modems c. 1980 2400 Modems c. 1990 9600 Serial terminals 19200 38400 Typical maximum.

#### 3.Write short notes about the communication protocols in detailed manner?

#### **Communication Protocols**

(1) parallel data transmission ieee-488 Parallel (HPIB or GPIB ) Centronics Parallel Protocol (Printer ) SCSI IDE ISA (Industrial Standard Architecture, 16 bit) PCI (Referral Component Interconnect, 32 bit) AGP

(2) serial data transmission RS 232 RS 422 RS 485 UART (Universal Asynchronous receiver-transmitter) USART (Universal Synchronous- Asynchronous receiver-transmitter) MIDI IEEE1394, also called "FireWire" CAN (Controller Area Network) USB (Universal Serial Bus) I 2 C (Inter Integrated Circuit) -- Philips SPI (Serial Peripheral Interface bus) Micro-wire Ethernet Fiber optics Bluetooth wifi sub sections to parallel and SERIAL protocols Wired connections Wireless connections Radio Frequency (RF) infrared (ir) how to selection a protocol or to develop your own Amount of data Speed of processor Hardware or software implementation Number of available pins Number of sensor Introduction to Communication Interface Parallel Communication Interface (PCI) Synchronous Asynchronous Serial Communication Interface (SCI)

Parallel ports were originally developed by IBM as a way to connect a printer to a PC. When IBM was in the process of designing the PC, the company wanted the computer to work with printers offered by Centronics, a top printer manufacturer at the time. IBM decided not to use the same port interface on the computer that Centronics used on the printer. Instead, IBM engineers coupled a 25-pin connector, DB-25, with a 36-pin Centronics connector to create a special cable to connect the printer to the computer. Other printer manufacturers ended up adopting the Centronics interface, making this strange hybrid cable an unlikely de facto standard. When a PC sends data to a printer or other device using a parallel port, it sends 8 bits of data (1 byte) at a time. These 8 bits are transmitted parallel to each other. The standard parallel port is capable of sending 50 to 100 kilobytes of data per second. Advantages of Parallel Data Transmission: <sup>3</sup>/<sub>4</sub>Fastest form of transmission -- able to send multiple bits simultaneously <sup>3</sup>/<sub>4</sub>doesn't require high frequency of operation Disadvantages of Parallel Data Transmission: <sup>3</sup>/<sub>4</sub>Requires separate lines for each bit of a word <sup>3</sup>/<sub>4</sub>Costly to run long distances due to multiple wires <sup>3</sup>/<sub>4</sub>Suffers from electromagnetic interference <sup>3</sup>/<sub>4</sub>Cable lengths more limited than a serial cable Applications: Parallel ports can be used to connect a host of popular computer peripherals: such as prints, scanners, CD burners, external hard drives, Iomega zip, network adapters, and tape backup drives. Types of parallel port At the present time it is known four types of parallel port: o Standard parallel port (SPP) o Parallel port PS/2 (bidirectional) o Enhanced Parallel Port (EPP) o Extend Capability Port (ECP) SPP/EPP/ECP The original specification for parallel ports was unidirectional, meaning that data only traveled in one direction for each pin. With the introduction of the PS/2 in 1987, IBM offered a new bidirectional parallel port design. This mode is commonly known as Standard Parallel Port (SPP) and has completely replaced the original design. Bidirectional communication allows each device to receive data as well as transmit it. Many devices use the eight pins (2 through 9) originally designated for data. Using the same eight pins limits communication to half-duplex, meaning that information can only travel in one direction at a time. But pins 18 through 25, originally just used as grounds, can be used as data pins also. This allows for full-duplex (both directions at the same time) communication. Enhanced Parallel Port (EPP) was created by Intel, Xircom, and Zenith in 1991. EPP allows for much more data, 500 kilobytes (KB) to 2 megabytes (MB), to be transferred each second. It was targeted specifically for non-printer devices that would attach to the parallel port, particularly storage devices that needed the highest possible transfer rate.

#### 4.Write short notes about the serial communication in detailed manner?

#### Serial Data Transmission:

- Synchronous Data Transmission: Data is transmitted one bit at a time, using a clock to maintain integrity between words. Advantages: <sup>3</sup>/<sub>4</sub>Only one (half duplex) or two (full duplex) wires are required to send/receive data. <sup>3</sup>/<sub>4</sub>Low cost due to low number of wires. Disadvantages: <sup>3</sup>/<sub>4</sub>Lower speeds than parallel transmissions. <sup>3</sup>/<sub>4</sub>Difficult to maintain data integrity due to problems with synchronizing clocks.

- 2. Asynchronous Data Transmission: Data is transmitted on bit at a time using start bits and strop bits to maintain integrity between words.

Disadvantages: <sup>3</sup>/<sub>4</sub>Lower speeds than parallel transmissions. Key words for SCI Baud Rate: The measure of the number of signal elements transmitted or received per second. Baud rates and data bit rates (bps-bit per second) are not equal in asynchronous transmission due to the start and stop bits. Start Bit: The bit preceding every word that signals the receiver a data word is coming.

In some microcontroller (e.g., HC11) the start bit is logic low (0), while in others the start bit is logic high

(1). Parity Bit: A bit sometimes added to the end of the data word. There are three possible settings for the parity: none, even, and odd. The setting represents the sum of the 1's transmitted. Stop Bit: The bit or bits following every word that signals the end of a data word. In some microcontroller (e.g., HC11) the stop bit is logic high (1), while in others the start bit is logic low (0).

**Half Duplex**: Two-way serial communication using only one line. With half duplex, the device can not transmit and received at the same time.

**Full Duplex**: Two-way serial communication using two lines. With full duplex, data can be simultaneously transmitted and received. Applications of SCI <sup>3</sup>/<sub>4</sub>The SCI can be used to transmit/receive data through a modern. <sup>3</sup>/<sub>4</sub>The SCI can be used to transmit/receive data with any device that uses RS-232-C protocol.

#### 5.Write short notes about the serial communication standards in detailed manner?

- 1.RS-485

- 2. RS-485

- 3.RS-422

RS422 is an improved RS-422 with the capability to connect up to 16 devices (transceivers) on one serial bus to form a network. Such a network can have a "daisy chain" topology where each device is connected to two other devices except for the devices on the ends.

Only one device may drive data onto the bus at a time. The standard does not specify the rules for deciding who transmits and when on such a network.

That's up to the system designer to define. RS-423 RS-423 is similar to RS-232C except that it allows for higher baud rates and longer cable lengths because it tolerates ground voltage differences between sender and receiver.

The maximum signal voltage levels are  $\pm 6$  volts. Ground voltage differences can occur in electrically noisy environments where heavy electrical machinery is operating. RS-422 RS-422, like RS-232, is used to connect only two systems.

It uses differential, or "double ended" data transmission, which means that data is transmitted simultaneously on two wires between two stations independent of the ground wire. Each signal requires 2 wires with a ground present in the system.

The advantage of this method over RS-232 is higher speeds and longer cable lengths - 4000 feet at a 100K baud rate, for example.

#### **<u>6.Write short notes about the CAN bus in detailed manner?</u>**

Controller Area Network (CAN) is a network protocol developed by Bosch for vehicle systems, but which is coming into use for linking distributed controllers, sensors etc in other fields. Bosch have published a specification .

CAN is a CSMA/CD protocol (some sources have CSMA/CR for similar protocols) that uses non-return to zero coding with bit stuffing. It supports speeds of up to 1Mb/s so is an SAE class C protocol, suitable for real time control applications.

Messages are not addressed to intended recipients, but the sender's identifier is included, and this tells the receivers what data it contains so the receiver ignores it if it is not interested. Messages are given a priority according to the sender's address, so the priority of messages is decided at the design stage.

In the spec there are two standards for CAN 2.0, imaginatively called A and B. These differ in message format, B has an extended message format, with a 29 bit identifier, as opposed to A's 11 bit one.

CAN, the CAN devices add filtration of the messages, so a controller is only interrupted by those messages the filter passes, that is those of interest to that controller.

CANbus in Automobile Electrical and Electronic Systems draw attention to the difference between having a local intelligent control module (for example, for all functions located in the driver's door) and having the intelligence actually in the actuators, so control is distributed, and each actuator (and each sensor) is on the bus itself.

#### Network access, collision detection and resolution

Binary zero is represented by a "dominant" state in the bus and binary one by a recessive state, so a binary zero takes precedence over a one, so lower numbered identifiers have priority over higher numbered ones.

CAN is a CSMA/CD protocol. If the network is idle, any node can send a message. If two messages are sent simultaneously, the node that sends a recessive bit, but detects a dominant bit stops transmitting, leaving the network free for the higher priority message. The higher priority message is not corrupted (Non-destructive bitwise arbitration). As this strategy resolves collisions and does not merely detect them, some sources describe protocols with a similar collision strategy as CSMA/CR, Carrier Sense Multiple Access/Collision Resolution. The identifier and RTR fields are used for collision arbitration. Therefore arbitration breaks down if two nodes can send data (as opposed to remote request) messages with the same identifier, as the clash will not be identified until later in the message, giving rise to a bit error. Each node must send data messages with a unique identifier. This has the side effect that if, say, all four road wheels had rotation sensors would each need their own identifier, so they would have an order of priority. It seems to me not unreasonable to suggest that this could lead to conflicts in designing the system, which I do not propose to discuss here as it is outside the scope of the project the network once the current message transmission is complete. The second highest priority message is guaranteed access after that, provided the top priority message source doesn't broadcast continuously, so this is pretty much guaranteed. Surely, however, as one moves down the order of priority, eventually one is going to reach a point where a high priority source might be ready to transmit again while a low priority source is still waiting, so its latency is not guaranteed.

#### 7.Explain the error detection method by using CAN bus in detailed manner?

#### **Error detection**

There are 5 error detection mechanisms: -

- Cyclic redundancy check. Each message contains a 15 bit CRC code computed by sender and checked by receivers, who will flag any errors. More in the spec (in black binder)

- 2. Frame check. At certain points in the frame, the correct value is predefined.

- 3. ACK(nowledgement) Error Check. If transmitter determines an error has not been acknowledged, an ACK error is flagged.

- 4. Bit Monitoring. A transmitter checks the network and flags a bit error if the value on the bus is not that sent. This does not happen during transmission of the identifier field, of course, as that is how a collision is detected.

- 5. Bit stuffing After 5 consecutive bits of the same value, a bit of the opposite value is added to the frame.

If an error is detected, an error frame is sent, aborting the transmission.

Error confinement provides a mechanism for distinguishing between temporary and permanent errors. Each node has two error counters (for transmit and receive) which are

incremented when errors are found. It is covered in more detail in the spec but briefly each receive error increments its counter by one, and each transmit error increments its counter by 8. If either counter goes above 127 the node concerned goes into "error passive" mode. In this mode it can still transmit and receive messages, but is restricted in flagging errors. If a device's transmit error counter goes above 255, the device will go into "bus off" mode and will cease to be active. This condition will clearly need to be modelled in simulating CANbus systems for FMEA. This seems to imply that we must allow for the modelling of repeat errors or for modelling the network as though the counter(s) had reached a level such that devices were going into "bus off" mode.

#### Bit timing and synchronisation

This is covered in the spec of course, and there is an introduction to this in the Omegas material . Briefly, a bit time consists of four non-overlapping segments, Sync-seg, Prop-seg, Phase-seg1 and Phase-seg2. An edge should lie within Sync-seg, while Prop-seg is used to compensate for delay times in the network. It is therefore the sum of twice the signal propagation time on the bus, the input comparator delay and the output driver delay, so is characteristic to the network. Phase-seg1 and Phase-seg2 are used to compensate for edge phase errors. They can be lengthened or shortened by resynchronisation. The sampling point is the boundary between Phase-seg1 and Phase-seg2. As non-return to zero encoding is used, there need not be an edge during Sync-seg, but bit stuffing ensures that there will be an edge after five edge-free ones.

#### CAN in the ISO/OSI stack and higher level protocols

The scope of the CANbus protocol covers the physical and data link layers of the ISO/OSI model. to three levels in the CANbus protocol; physical layer, transfer layer and object layer. The physical layer is not defined in the Bosch spec, but is typically shielded or unshielded twisted pair. Idle state is both lines at +2.5 volts. A dominant bit reduces one line, known as CAN\_L, to zero, while increasing the other line (CAN\_H) to +5 volts while a recessive bit is close to the idle value, with CAN\_L slightly above CAN\_H, so is "over written" by a dominant bit. A standard for the physical layer of a 500 KBPS vehicle network is defined in SAE J2284-500 .The transfer and object layers between them comprise all the services and functions of the ISO/OSI data link layer.

The Can in Automation (CiA) trade organisation supports various higher level protocols

- CANopen

- DeviceNet

- CAL (CAN application layer)

- CAN Kingdom

- SDS (Smart Distributed System)

CiA is an organisation mainly interested in using CAN for industrial automation so it may well be that the protocols listed above are more common in that field than in the automotive field.

#### **<u>8.Explain the input output port types in detailed manner?</u>**

#### **UART protocol serial line format**

Starting point of receiving the bits for each byte is indicated by a line transition from 1 to 0 for a period = T. [T - 1 called baud rate.] If sender's shift-clock period = T, then a byte at the port is received at input in period = 10.T or 11.T due to use of additional bits at start and end of each byte

#### **UART protocol serial line format**

Receiver detects n bits at the intervals of T from the middle of the start indicating bit. The n = 0, 1, ..., 10 or 11 and finds whether the data-input is 1 or 0 and saves the bits in an 8bit shift register. Processing element at the port (peripheral) saves the byte at a port register from where the microprocessor reads the byte.

#### **Asynchronous Serial Output**

Asynchronous output serial port line TxD (transmit data). Each bit in each byte transmit at fixed intervals but each output byte is not in synchronization (separates by a variable interval or phase difference). Minimum separation is 1 stop bit interval

Does not send the clock pulses along with the bits. Sender transmits the bytes at the minimum intervals of n.T. Bits receiving starts from the middle of the start indicating bit, n = 0, 1, ..., 10 or 11 and sender sends the bits through a 10 or 11 -bit shift register.

The processing element at the port (peripheral) sends the byte at a port register to where the microprocessor is to write the byte. Synchronous serial output is also called UART output if serial output is according to UART protocol

#### **Types of Serial ports**

Synchronous Serial Input

Synchronous Serial Output

Asynchronous Serial UART input

Asynchronous Serial UART output

Both as input and as output, for example, modem.

#### **Types of parallel ports**

Parallel port one bit Input Parallel one bit output Parallel Port multi-bit Input Parallel Port multi-bit Output

#### synchronous Serial Input

Synchronous Serial Input The sender along with the serial bits also sends the clock pulses SCLK (serial clock) to the receiver port pin. The port synchronizes the serial datainput bits with clock bits. Each bit in each byte as well as each byte in synchronization

Synchronization means separation by a constant interval or phase difference. If clock period = T, then each byte at the port is received at input in period = 8T. The bytes are received at constant rates. Each byte at input port separates by 8T and data transfer rate for the serial line bits is (1/T) bps. [1bps = 1 bit per s]

#### Synchronous Serial Input Example

Inter-processor data transfer, reading from CD or hard disk, audio input, video input, dial tone, network input, transceiver input, scanner input, remote controller input, serial I/O bus input, writing to flash memory using SDIO (Secure Data Association IO based card)

#### 9.Explain the serial peripheral interface (SPI) in detailed manner?

SPI = Simple, 3 wire, full duplex, synchronous serial data transfer Interfaces to many devices, even many non-SPI peripherals Can be a master or slave interface

4 interface pins: -MOSI master out slave in MISO master in slave out SCK serial clock SS\_n slave select 3 registers: 1.SPCR control register 2.SPSR status register 3.SPDR data register Serial Peripheral Interface (SPI)

Serial Peripheral Interface (SPI) SPI "Gotchas" "Now my board won't program." SPI shares SCK with programming interface. If it won't program anymore, you likely messed up SCK. "SPI acts totally wierd." Often a symptom of SS\_n being configured as an input and being left to float or allowed to go high.

SPI goes in and out between slave and master modes"SPI device interactions:" When programming, the programmer first does a chip reset. When the mega128 resets, all pins are set to input with high impedance (floating). If a SPI device is on the SPI bus, its chip-select may float low and enable the device, and SPI data will crash the programming data. Adding a pull-up resistor to chip selects will solve this problem.

the SPI clock to run, a "dummy" write is made to the SPI SPDR register. This starts the clock running so the data on MISO is brought into the uC. If no peripherals are selected, the outgoing data will be ignored. If you are clever, you can send data out and bring data in at the same time.

spi\_read //Reads the SPI port.

uint8\_t spi\_read(void){ SPDR = 0x00;

//"dummy" write to SPDR while (bit\_is\_clear(SPSR,SPIF)){}

//wait till 8 clock cycles are done return(SPDR);

//return incoming data from SPDR }//read\_spi

Serial Peripheral Interface (SPI) SPI Application - Code

spi\_init //Initializes the SPI port on the mega128. Does not do any further //

external device specific initializations.

/ void spi\_init(void) { DDRB = 0x07;

//Turn on SS, MOSI, SCLK (SS is output)

# **10.Explain the device driver in detailed manner?**

#### **Block and character devices**

- Block devices include disk drives

- Commands include read, write, seek

- Raw I/O or file-system access

- Memory-mapped file access possible

- Character devices include keyboards, mice, serial ports

- Commands include get, put

- Libraries layered on top allow line editing

#### **Network devices**

- Different enough from the block & character devices to have own interface

- Unix and Windows/NT include socket interface Separates network protocol from network operation

- Approaches vary widely (pipes, FIFOs, streams, queues, mailboxes

## **Clocks and timers**

- Provide current time, elapsed time, timer

- if programmable interval time used for timings, periodic interrupts

- ioctl (on UNIX) covers odd aspects of I/O such as clocks and timers Blocking and nonblocking I/O

- Blocking process suspended until I/O completed Easy to use and understand Insufficient for some needs

- Nonblocking I/O call returns as much as available User interface, data copy

(buffered I/O) – Implemented via multi-threading – Returns quickly with count of

bytes read or written

Asynchronous - process runs while I/O executes – Difficult to use – I/O subsystem signals process when I/O completed

## Device driver design issues

- Operating system and driver communication

- Commands and data between OS and device drivers

- Driver and hardware communication Commands and data between driver and hardware

- Driver operations Initialize devices Interpreting commands from OS Schedule multiple outstanding requests – Manage data transfers – Accept and process interrupts – Maintain the integrity of driver and kernel data structures

# Device driver interface

- Open( deviceNumber ) Initialization and allocate resources (buffers)

- Close( deviceNumber ) Cleanup, deallocate, and possibly turnoff

- Device driver types Block: fixed sized block data transfer Character: variable sized data transfer Terminal: character driver with terminal control Network: streams for networking

# <u>UNIT III</u>

# **<u>1.Write the short notes about the EDLC in detail manner?</u>**

EMBEDDED PRODUCT DEVELOPMENT LIFE CYCLE (EDLC)

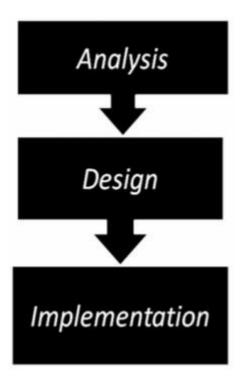

EDLC is Embedded Product Development Life Cycle

It is an Analysis – Design – Implementation based problem solving approach for embedded systems development.

There are three phases to Product development:

Analysis involves understanding what product needs to be developed

- Design involves what approach to be used to build the product

- Implementation is developing the product by realizing the design.

**Need for EDLC**

- EDLC is essential for understanding the scope and complexity of the work involved in embedded systems development

- It can be used in any developing any embedded product

- EDLC defines the interaction and activities among various groups of a product development phase.

- Example:-project management, system design

# **Objectives of EDLC**

- The ultimate aim of any embedded product in a commercial production setup is to produce Marginal benefit

- Marginal is usually expressed in terms of Return On Investment

- The investment for product development includes initial investment, manpower, infrastructure investment etc.

- EDLC has three primary objectives are:

# Ensure that high quality products are delivered to user

- 1. Quality in any product development is Return On Investment achieved by the product

- 2. The expenses incurred for developing the product the product are:-

- 3. Initial investment

- 4. Developer recruiting

- 5. Training

- 6. Infrastructure requirement related

# Risk minimization defect prevention in product development through project management

- i. In which required for product development 'loose' or 'tight' project management

- ii. 'project management is essential for ' predictability co-ordination and risk minimization

- iii. Resource allocation is critical and it is having a direct impact on investment

- iv. Example:- Microsoft @ Project Tool

# Maximize the productivity

- i. Productivity is a measure of efficiency as well as Return On Investment

- ii. This productivity measurement is based on total manpower efficiency

- iii. Productivity in which when product is increased then investment is fall down,Saving manpower

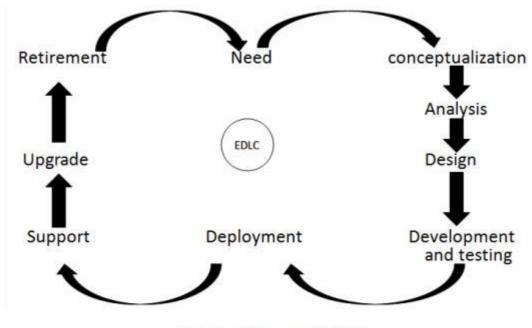

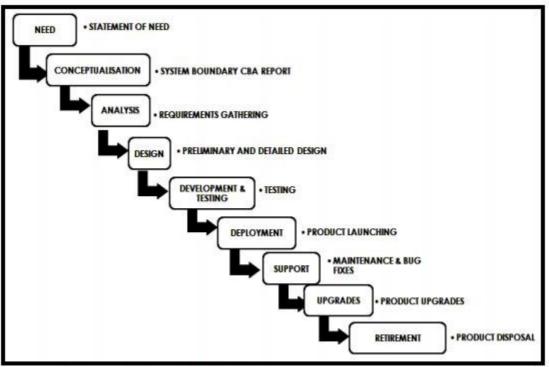

# 2.Write the short notes about the different phases of EDLC in detail manner?

# different phases of edlc

The following figure depicts the different phases in EDLC:

Figure : Phases of EDLC

## Need

- The need may come from an individual or from the public or from a company.

- 'Need' should be articulated to initiate the Development Life Cycle; a 'Concept Proposal' is prepared which is reviewed by the senior management for approval.

# Need can be visualized in any one of the following three needs:

- New or Custom Product Development.

- Product Re-engineering.

- Product Maintenance.

# Conceptualization

Defines the scope of concept, performs cost benefit analysis and feasibility study and prepare project management and risk management plans.

# The following activities performed during this phase:

Feasibility Study : Examine the need and suggest possible solutions.

**Cost Benefit Analysis (CBA):** Revealing and assessing the total development cost and profit expected from the product.

**Product Scope:** Deals with the activities involved in the product to be made.

**Planning Activities:** Requires various plans to be developed first before development like Resource Planning & Risk management Plans.

# Analysis

The product is defined in detail with respect to the inputs, processes, outputs, and interfaces at a functional level.

The various activities performed during this phase..

• Analysis and Documentations: This activity consolidates the business needs of the product under development.

• Requirements that need to be addressed..

Functional Capabilities like performance  $\theta$

Operational and non-operational quality attribute  $\theta$

Product external interface requirements  $\theta$

User manuals  $\theta$  Data requirements  $\theta$

Operational requirements  $\theta$

Maintenance requirements  $\theta$

General assumptions  $\theta$

**Defining Test Plan and Procedures**: The various type of testing performed in a product development are:

Unit testing – Testing Individual modules

Integration testing – Testing a group of modules for required functionality

System testing-Testing functional aspects or functional requirements of the product after integration

User acceptance testing- Testing the product to meet the end user requirements.

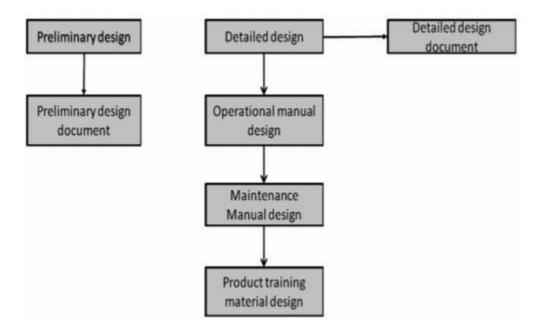

## Design

The design phase identifies application environment and creates an overall architecture for the product.

It starts with the Preliminary Design. It establishes the top level architecture for the product. On completion it resembles a 'black box' that defines only the inputs and outputs. The final product is called Preliminary Design Document (PDD).

Once the PDD is accepted by the End User the next task is to create the 'Detailed Design'.

It encompasses the Operations manual design, Maintenance Manual Design and Product Training material Design and is together called the 'Detailed Design Document'.

# 3.Write the short notes about the testing and development procedure of EDLC in detail manner?

# **Development and Testing**

Development phase transforms the design into a realizable product.

The detailed specification generated during the design phase is translated into hardware and firmware.

The Testing phase can be divided into independent testing of firmware and hardware that is:

- Unit testing

- Integration testing

- System testing

- User acceptance testing

# Deployment

Deployment is the process of launching the first fully functional model of the product in the market.

It is also known as First Customer Shipping (FCS).

# Tasks performed during this phase are:

# Notification of Product Deployment: Tasks performed here include:

Deployment schedule

- Brief description about the product

- Targeted end user

- Extra features supported

- Product support information

## **Execution of training plan**

Proper training should be given to the end user top get them acquainted with the new product.

## **Product installation**

Install the product as per the installation document to ensure that it is fully functional.

## **Product post Implementation Review**

After the product launch, a post implementation review is done to test the success of the product.

## Support

- The support phase deals with the operational and maintenance of the product in the production environment.

- Bugs in the product may be observed and reported.

- The support phase ensures that the product meets the user needs and it continues functioning in the production environment.

- Activities involved under support are

**Setting up of a dedicated support wing**: Involves providing 24 x 7 supports for the product after it is launched.

Identify Bugs and Areas of Improvement: Identify bugs and take measures to eliminate them.

Upgrades

- Deals with the development of upgrades (new versions) for the product which is already present in the market.

- Product upgrade results as an output of major bug fixes.

- During the upgrade phase the system is subject to design modification to fix the major bugs reported.

# **Retirement/Disposal**

- The retirement/disposal of the product is a gradual process.

- This phase is the final phase in a product development life cycle where the product is declared as discontinued from the market.

- The disposal of a product is essential due to the following reasons

- Rapid technology advancement

- Increased user needs

# 4 eldc approaches

Following are some of the different types of approaches that can be used to model embedded products.

- 1. Waterfall or Linear Model

- 2. Iterative/ Incremental or Fountain Model

- 3. Prototyping Model

- 4. Spiral Model

# 4.Describe the types of models in EDLC in detail manner?

- 1 Introduction

- 2 Waterfall or Linear Model

- 3 Iterative/ Incremental or Fountain Model

- 4 Prototyping Model

- 5 Spiral Model

# **OBJECTIVES**

After reading this chapter you will understand:

Some EDLC Models like:

- Waterfall or Linear Model

- Iterative/ Incremental or Fountain Model

- Prototyping Model,Spiral Model

## embedded development life cycle

Objectives

1 Introduction

2 EDLC

- Need For ELDC

- Objectives

3 Different Phases of EDLC

4 ELDC Approaches

## **OBJECTIVES**

- After Reading this chapter you will understand

- The Embedded Development Life Cycle

- Phases Involved in the EDLC

The SDLC used in Software Development, there is EDLC used in Embedded product development. This chapter explains what is the EDLC, its objectives, the phases that are involved in the EDLC.

## 5.Describe the waterfall models in detail manner?

## waterfall model

- Linear or waterfall model is the one adopted in most of the olden systems.

- In this approach each phase of EDLC (Embedded Development Product Lifecycle) is executed in sequence.

- It establishes analysis and design with highly structured development phases.

- The execution flow is unidirectional.

- The output of one phase serves as the input of the next phase

- All activities involved in each phase are well planned so that what should be done in the next phase and how it can be done.

- The feedback of each phase is available only after they are executed.

- It implements extensive review systems To ensure the process flow is going in the right direction.

- One significant feature of this model is that even if you identify bugs in the current design the development process proceeds with the design.

- The fixes for the bug are postponed till the support phase.

Product development is rich in terms of:

- Documentation

- Easy project management

- Good control over cost & Schedule

## Drawbacks

It assumes all the analysis can be done without doing any design or implementation

- The risk analysis is performed only once.

- The working product is available only at the end of the development phase

- Bug fixes and correction are performed only at the maintenance/support phase of the life cycle.

# Figure: Waterfall Model

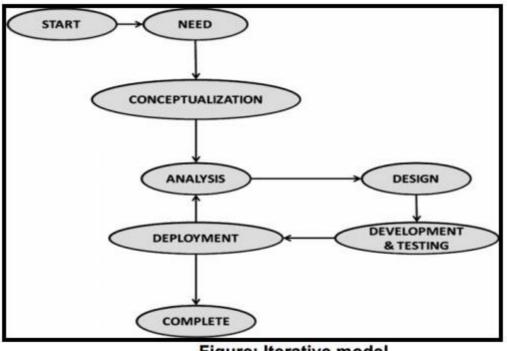

# 6.Describe the iterative models of EDLC in detail manner?

## Iterative / incremental or fountain model

- Iterative and Incremental development is at the heart of a cyclic software development process developed in response to the weaknesses of the waterfall model.

- The iterative model is the repetitive process in which the Waterfall model is repeated over and over to correct the ambiguities observed in each iteration.

Figure: Iterative model

The above figure illustrates the repetitive nature of the Iterative model.

- The core set of functions for each group is identified in the first cycle, it is then built, deployed and release. This release is called as the first release.

- Bug fixes and modification for first cycle carried out in second cycle.

- Process is repeated until all functionalities are implemented meeting the requirements.

# Advantages

- Good development cycle feedback at each function/feature implementation

- Data can be used as reference for similar product development in future.

- More responsive to changing user needs.

- Provides working product model with at least minimum features at the first cycle.

- Minimized Risk

- Project management and testing is much simpler compared to linear model.

- Product development can be stopped at any stage with a bare minimum working product.

# Disadvantages

- Extensive review requirement each cycle.

- Impact on operations due to new releases.

- Training requirement for each new deployment at the end of each development cycle.

- Structured and well documented interface definition across modules to accommodate changes

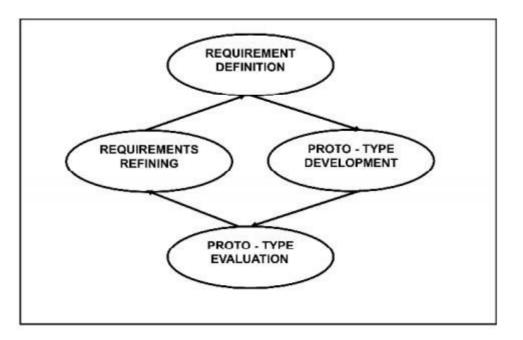

# 7.Describe the prototyping models of EDLC in detail manner?

## prototyping model

- It is similar to iterative model and the product is developed in multiple cycles.

- The only difference is that, Prototyping model produces a refined prototype of the product at the end of each cycle instead of functionality/feature addition in each cycle as performed by the iterative model.

- There won't be any commercial deployment of the prototype of the product at each cycle's end.

- The shortcomings of the proto-model after each cycle are evaluated and it is fixed in the next cycle.

- After the initial requirement analysis, the design for the first prototype is made, the development process is started.

- $\circ$  On finishing the prototype, it is sent to the customer for evaluation.

- The customer evaluates the product for the set of requirements and gives his/her feedback to the developer in terms of shortcomings and improvements needed.

- The developer refines the product according to the customer's exact expectation and repeats the proto development process.

- After a finite number of iterations, the final product is delivered to the customer and launches in the market/operational environment

- the product undergoes significant evolution as a result of periodic shuttling of product information between the customer and developer

The prototyping model follows the approach

- Requirement definition

- Proto-type development

- Proto-type evaluation

- Requirements refining

Figure: Prototyping Model

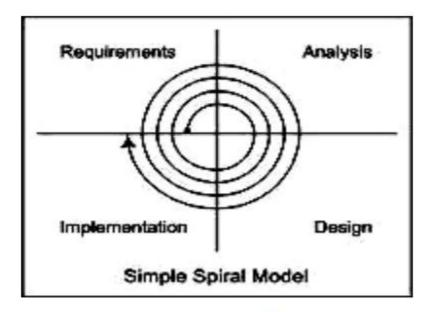

# 8.Describe the spiral models of EDLC in detail manner?

## spiral model

- Spiral model is developed by Barry Boehm in 1988.

- The Product development starts with project definition and traverse through all phases of EDLC(Embedded Product Development Life Cycle).

The activities involved are:

- Determine objectives, alternatives, constraints

- Evaluate alternatives, identify and resolve risks

It is a combines the concept of Linear Model and iterative nature of Prototyping Model.

- In prototyping after the requirement analysis the design for the prototype is made and development process is started.

- On finishing the prototype it is send to the customer for evaluation ie. Judgment.

- After customer evaluation for the product the feedback is taken from the customer in term of what improvement is needed.

- $\circ$  Then developer refines the product according to the customer expectation.

Spiral Model contains the concept of linear model, having following type.

- Requirement

- Analysis

- Design

- Implementation

**Figure: Spiral Model**

# **Requirement:**

• This process is focused specifically on embedded software, to understand the nature of the software to be build and what are the requirement for the software. And the requirement for both the system & the software is documented & viewed to customer.

# Analysis:

- Analysis is performed to develop a detailed functional module under consideration.

- The product is defined in detailed with respect to the input, processing & output.

- This phase emphasis on determining 'what function must be performed by the product' & how to perform those function.

# Design:

- Product design deals with the entire design of the product taking the requirement into consideration.

- The design phase translates requirement into representation.

## Implementation:

- The launching of first fully functional model of the product in the market is done or handing over the model to an end user/client

- modifications are implemented & product is made operational in production environment.

## 9.Explain the different types of trends in embedded systems?

## Objectives

- 1 Introduction

- 2 Processor Trends

- 3 Operating System Trends

- 4 Development Language Trends

- 5 Open Standards, Frameworks and alliances

- 6 Bottlenecks faced by Embedded Industry

Different trends in the embedded industry related to:

- Processor Trends

- Operating System Trends

- Development Language Trends

- Open Standards, Frameworks and alliances

- Bottlenecks faced by Embedded Industry

## processor trends

There have been tremendous advancements in the area of processor design.

Following are some of the points of difference between the first generation of processor/controller and today's processor/ controller.

**Number of ICs per chip**: Early processors had a few number of IC/gates per chip. Today's processors with Very Large Scale Integration (VLSI) technology can pack together ten of thousands of IC/gates per processor.

**Need for individual components:** Early processors need different components like brown out circuit, timers, DAC/ADC separately interfaced if required to be used in the circuit. Today's processors have all these components on the same chip as the processor.

**Speed of Execution:** Early processors were slow in terms of number of instructions executed per second. Today's processor with advanced architecture support features like instruction pipeline improving the execution speed.

**Clock frequency:** Early processors could execute at a frequency of a few MHz only. Today's processors are capable of achieving execution frequency in rage of GHz.

**Application specific processor:** Early systems were designed using the processors available at that time. Today it is possible to custom create a processor according to a product requirement.

# Following are the major trends in processor architecture in embedded development.

## System on Chip (SoC)

- This concept makes it possible to integrate almost all functional systems required to build an embedded product into a single chip.

- SoC are now available for a wide variety of diverse applications like Set Top boxes, Media Players, PDA, etc.

- SoC integrate multiple functional components on the same chip thereby saving board space which helps to miniaturize the overall design.

## **Multicore Processors/ Chiplevel Multi Processor**

This concept employs multiple cores on the same processor chip operating at the same clock frequency and battery.

Based on the number of cores, these processors are known as:

Dual Core – 2 cores Tri Core – 3 cores

$Quad\ Core-4\ cores$

These processors implement multiprocessing concept where each core implements pipelining and multithreading.

## **Reconfigurable Processors**

- It is a processor with reconfigurable hardware features.

- Depending on the requirement, reconfigurable processors can change their functionality to adapt to the new requirement. Example: A reconfigurable processor chip can be configured as the heart of a camera or that of media player.

- These processors contain an Array of Programming Elements (PE) along with a microprocessor. The PE can be used as a computational engine like ALU or a memory element.

## operating system trends

• The advancements in processor technology have caused a major change in the Embedded Operating System Industry.

- There are lots of options for embedded operating system to select from which can be both commercial and proprietary or Open Source.

- Virtualization concept is brought in picture in the embedded OS industry which replaces the monolithic architecture with the microkernel architecture.

- This enables only essential services to be contained in the kernel and the rest are installed as services in the user space as is done in Mobile phones.

- Off the shelf OS customized for specific device requirements are now becoming a major trend.

## development language trends

There are two aspects to Development Languages with respect to Embedded Systems Development

## **Embedded Firmware**

- It is the application that is responsible for execution of embedded system.

- It is the software that performs low level hardware interaction, memory management etc on the embedded system.

# **Embedded Software**

- It is the software that runs on the host computer and is responsible for interfacing with the embedded system.

- It is the user application that executes on top of the embedded system on a host computer.

- Early languages available for embedded systems development were limited to C & C+ + only. Now languages like Microsoft C\$, ASP.NET, VB, Java, etc are available.

# **10.Explain** the design process of embedded systems in detailed manner?

## The embedded system design process

Overview of the embedded system design process aimed at two objectives. First, it will give us an introduction to the various steps in embedded system design before we delve into them in more detail. Second, it will allow us to consider the design *methodology* itself. summarizes the major steps in the embedded system design process. In this top-down view, we start with the system *requirements* in the next step comes *Specification*.

**Top-down Design**—we will begin with the most abstract description of the system and conclude with concrete details. The alternative is a **bottom-up** view in which we start with components to build a system. Bottom-up design steps are shown in the figure as dashed-line arrows. We need bottom-up design because we do not have perfect insight into how later stages of the design process will turn out. During the design process we have to consider the major goals of the design such as

- manufacturing cost;

- performance (both overall speed and deadlines); and

- power consumption.

Design steps are detailed below:

## A.Requirements: